Hindawi Journal of Electrical and Computer Engineering Volume 2019, Article ID 1675169, 8 pages https://doi.org/10.1155/2019/1675169

# Research Article

# **An Ultra-Low Power Parity Generator Circuit Based on QCA Technology**

# Ismail Gassoumi , Lamjed Touil, Bouraoui Ouni , and Abdellatif Mtibaa 1

<sup>1</sup>Laboratory of Electronics and Microelectronics, University of Monastir, Monastir, Tunisia

Correspondence should be addressed to Ismail Gassoumi; gassoumiismail@gmail.com

Received 28 June 2019; Revised 2 September 2019; Accepted 12 September 2019; Published 7 October 2019

Guest Editor: Vítor Monteiro

Copyright © 2019 Ismail Gassoumi et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Quantum-dot cellular automata (QCA) technology is one of the emerging technologies that can be used for replacing CMOS technology. It has attracted significant attention in the recent years due to its extremely low power dissipation, high operating frequency, and a small size. In this study, we demonstrate an *n*-bit parity generator circuit by utilizing QCA technology. Here, a novel XOR gate is used in the synthesis of the proposed circuit. The proposed gate is based on electrostatic interactions between cells to perform the desired function. The comparison results demonstrate that the designed QCA circuits have advantages compared to other circuits in terms of cell count, area, delay, and power consumption. The QCADesigner software, as widely used QCA circuit design and verification, has been used to implement and to verify all of the designs in this study. Power dissipation has been computed for the proposed circuit using accurate QCAPro power estimator tool.

## 1. Introduction

The continuous scaling down of CMOS-based devices in size, over the past few decades, in accordance with Moore's law leads to many different and difficult challenges as recently these devices are becoming more resistant to scaling [1–3]. One of the biggest challenges faced by transistor-based circuits is power consumption from leakage current due to the increased threshold voltage and decreased supply voltage [4]. The search for new technologies led to quantum-dot cellular automata (QCA) which has appealing features such as lower energy consumption and less cell density [5]. QCA designs offer lower energy and area solutions to the existing CMOS logic [6, 7]. QCA-based designs are suitable for fabrication of nanoscale devices. In QCA, circuits are fabricated by quantum cells, and each cell contains four quantum dots as well as two electrons. Quantum dots are nanoscale structures which are constructed from semiconductors such as InAs and GaAs. Transferring information is achieved by propagation of a polarization state instead of current in QCA implementation. This new

technology attracted lot of researchers due to its direct use in quantum computing. Up to date, several works have been realized for the design of QCA logic circuits such as multipliers, adder, reversible ALU, divider, decoder, and memory circuits [8-15]. Many of these designs have advantages like faster speed and smaller size over their CMOS counterparts. In contrast, the mass production of ultra-small size QCA technology is very difficult. Additionally, QCA technology is prone to high error rates. The high error rate of this technology compared to traditional CMOS technology is due to the bridge, displacement, misalignment, and cell omission defects as well as stuck-at-fault which are likely occurred in the gates and interconnections. Defects can take place in both the chemical synthesis phase and the deposition phase. During the chemical synthesis phase, the QCA cells are manufactured, and during the deposition phase, the QCA cells are placed on a substrate. However, defects are more likely to occur in the deposition phase in which perfectly manufactured cells are imperfectly attached to the substrate. QCA devices are also susceptible to transient faults which are caused by thermodynamic effects,

<sup>&</sup>lt;sup>2</sup>Networked Objects Control & Communication Systems Lab, University of Sousse, Sousse, Tunisia

radiation, and other effects, such as the energy difference between the ground and the excited state is small.

In this framework, the exclusive-OR gate is probably a vital part of complex digital circuits since it is often operated as structural blocks in digital fabrication. It can be used in the development of specific communication circuits such as parity generator and checker. QCA is one of the important technologies that enable high performance circuit design with low power consumption features. In this context, the exclusive-OR gate presents an important component. Various QCA-based exclusive-OR gates have been proposed in the literature, which have been designed using the majority gate-based methodology. In order to reduce power consumption and hardware complexity, this study presents an optimized QCA exclusive-OR gate, by which any complex digital designs may be synthesized. Additionally, an optimized parity generator circuit is achieved by using the proposed XOR gate. The main contributions of the paper are as follows:

- (i) An efficient design of QCA exclusive-OR gate is proposed

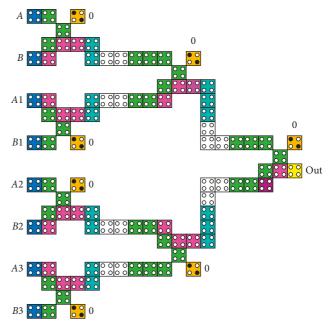

- (ii) The 4-, 8-, 16-, and 32-bit QCA parity generator circuits are designed using this proposed gate as a building block

- (iii) The designed circuits are simulated with QCADesigner software

- (iv) Power dissipation of the proposed designs has been estimated

The rest of the paper is organized as follows: In Section 2, the backgrounds of QCA technology are reviewed. In Section 3, our proposed exclusive-OR gate is presented and compared to the conventional exclusive-OR gates. In Section 4, parity generator circuits are designed by using the proposed gate, and are compared to other counterpart designs. The simulation results of the proposed designs have been presented in Section 5. Finally, Section 6 concludes the paper.

## 2. Background of QCA

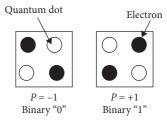

The basic functional block of QCA is the quantum cell that consists of four quantum dots. Each dot can hold one electron [6]. Electrostatic repulsions among the two electrons in the quantum cell make sure that the electrons can only reside in the antipodal sites. Thus, these electrons assume stable states, called polarizations, which are energetically equal and interpreted as binary "0" and "1" [16]. They have respective polarizations as P = "-1" (logic "0") and P = "+1" (logic "0") as shown in Figure 1. Polarization of the cells is calculated from equation (1) [17].

$$P = \frac{(\rho_1 + \rho_3) - (\rho_2 + \rho_4)}{\rho_1 + \rho_2 + \rho_3 + \rho_4},\tag{1}$$

where  $\rho_i$  shows the electric charge at the i th point. Binary information is displayed using the position of two electrons in each logical cell.

FIGURE 1: Two different polarizations of the quantum-dot cell.

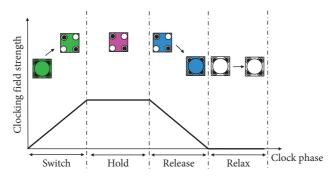

On the other hand, to ensure that proper data flow takes place, QCA circuit clocking is introduced [18]. QCA-based circuits have a four-phased clocking namely switch, hold, release, and relax as illustrated in Figure 2. These four phases are generated by the traveling electric field wave perpendicular to the QCA plane. The various clock zones are represented by four different colors. Clock zero is represented by green, clock one by pink, clock two by blue, and clock three by white. Each clocking zone has a phase shift of 90 with respect to the adjacent ones. Each cell in a clocking zone behaves as latch [19].

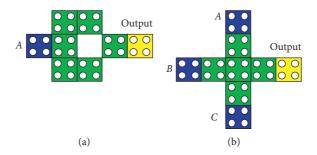

Furthermore, when placed close to each other, the polarization of one QCA cell influences the polarization of the other, again by Coulomb interaction. One can exploit this effect in order to construct logic gates, such as the NOT and the MAJ gates. The inverter is the result of placing the cells such that their vertices are touching as illustrated in Figure 3(a) [20]. A majority voter is made up of five cells: one device cell (center cell), three inputs, and an output cell as depicted in Figure 3(b). The majority voter is driven by three input drivers *A*, *B*, and *C*. Its output can be computed as follows:

$$MV(a,b,c) = AB + BC + AC.$$

(2)

Crossover types provide an advantage in circuit design in QCA as it offers a certain amount of design flexibility. QCA technology has two types of crossover. One, multilayer crossover and the other is coplanar crossover as depicted in Figures 4(a) and 4(b), respectively [16, 21]. The multilayer crossover yields high cost due to fabrication issue. In the second technique, two wires are overlapped in a similar plane to facilitate a simple binary wire cross an inverter chain.

### 3. Related Works

3.1. Previous QCA Exclusive-OR Circuits. Up to date, a widespread study in QCA has been outlined to achieve exclusive-OR designs [22–27] which are used in many of the digital logic circuits such as error detection circuits, arithmetic logic circuits, multiplexers, full adders, and comparators. The XOR gate is composed of two inputs and one output. Its output is true when two input operands are not the same, and the output is false otherwise.

In [22], the authors have proposed a novel low-power XOR gate. This designed gate consists of 13 cells and  $0.012 \, \mu \text{m}^2$  area. It occupies less area among the others. This

FIGURE 2: QCA clock zones.

FIGURE 3: Inverter gate (a) and majority gate (b).

FIGURE 4: Signal crossover schemes. (a) Coplanar crossing. (b) Multilayer crossing.

design is based on the interaction between cells for implementing the desired function. It does not include any crossover in its structure. In addition, there is no any majority gate, which leads to less number of cells and power consumption. In [23], the authors have presented a novel, robust exclusive-OR gate. This designed gate consists of 28 cells and  $0.02\,\mu\text{m}^2$  area. It is implemented without using any coplanar and multilayer crossover. This novel exclusive-OR design approach uses one five-input majority gate and two fixed polarization cells. The authors in [24] proposed a layout with 36 cells, extent  $0.030\,\mu\text{m}^2$ , and delay 0.75. This design is developed using a structure of coupled majority voter minority gate (CMVMIN), two majority gates, and two inverter gates. The design proposed in [25] requires 37 QCA cells, extent  $0.030\,\mu\text{m}^2$ , and delay 1. This

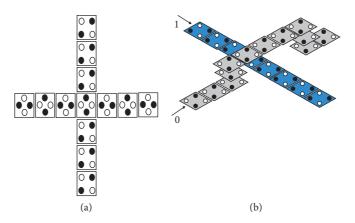

design has an important number of cells and provides a large area. Also, a novel design of the XOR gate has been proposed by Bahar et al. in [26]. This design has achieved a reduction in the number of used cells and area consumption. It consists of 12 QCA cells,  $0.02 \, \mu \text{m}^2$  extent, and 1.25 delay. Figure 5 shows some previous designed exclusive-OR gates.

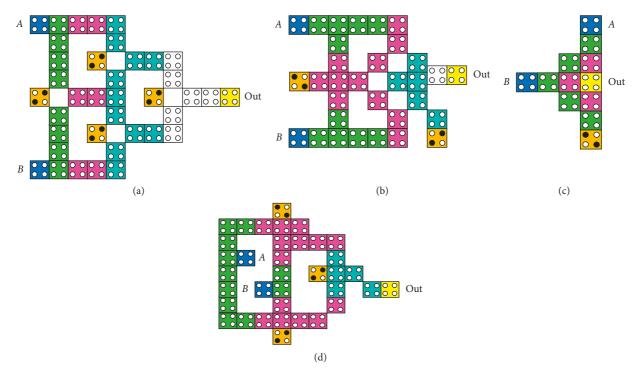

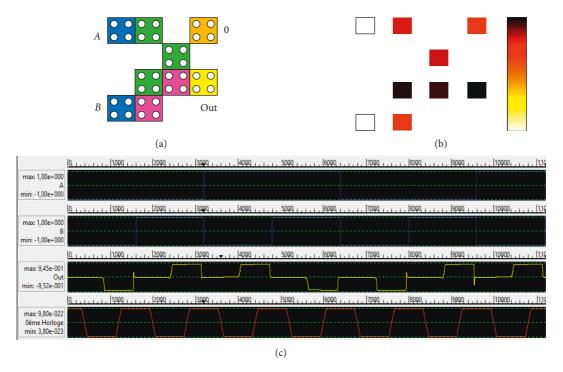

3.2. Proposed QCA Exclusive-OR Gate. In this section, a new efficient exclusive-OR gate is proposed by employing arranged and interacted QCA cells. The designed circuit and its simulation results are shown in Figures 6(a) and 6(c), respectively. Here, no majority gates are used to achieve the proposed design. The QCADesigner software is

FIGURE 5: Exclusive-OR gates: (a) design in [24], (b) design in [27], (c) design in [26], and (d) design in [23].

FIGURE 6: QCA layout of the designed (a) XOR gate, (b) power map, and (c) simulation outcomes.

used to verify the functionality of the designed circuit. The proposed QCA design covers only 9 cells, extent 0.01  $\mu$ m<sup>2</sup>, and a delay of 0.5. In contrast, the QCA layout proposed in [25] require 37 cells, extent 0.03  $\mu$ m<sup>2</sup>, and a delay of 1. Consequently, the designed XOR gate has an improvement

of 75.67%, 66.66%, and 50% in terms of cell complexity, extent, and delay, correspondingly, compared with the design in [25]. In addition, the proposed gate attains an advancement of 67.85%, 50%, and 33.33% in terms of cell intricacy, area, delay, and cost, respectively, compared with

FIGURE 7: QCA layout of the designed (a) 4 bit parity generator and (b) simulation outcomes.

the design in [23]. Thus, the proposed gate can lead to QCA digital designs with less hardware complexity and power consumption.

## 4. Parity Generator Designs

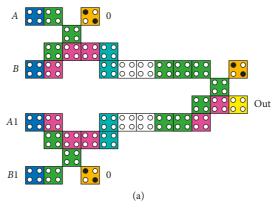

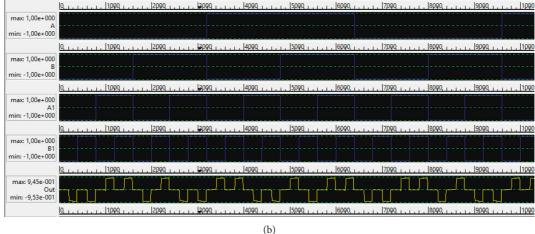

The logic parity generator is a fundamental component for information processing chips and computing systems, in which the accurate matching of all received and transmitted data needs to be verified. It plays an important role in the design of digital circuits. As a result, several attempts have been done to implement this important logic component, especially in the QCA technology [22, 23, 25, 27]. In this section, we propose a novel QCA circuit for the parity generator. Figure 7(a) shows the proposed logic block implementation of the proposed 4-bit parity generator circuit with three copies of the proposed QCA XOR gate. Figure 7(b) shows the simulation results of the proposed 4-bit parity generator circuit. The timing diagram indicates that the parity output is correctly obtained. It should be noted that this circuit can be easily extended to the n-bit QCA parity generator circuit. Figure 8 shows QCA implementation of the proposed 8 -bit parity generator circuit. In this focus, we demonstrate only the QCA layouts of 4- and 8-bit parity generator circuits because of the lack of space. Here, the cell count, area, and delay of the designed 4- and

FIGURE 8: QCA implementation of the proposed 8 bit parity generator circuit.

8-bit parity generator circuits are considerably improved compared to 4- and 8 bit parity generator circuits in [22, 23, 25].

## 5. Simulation Results and Comparison

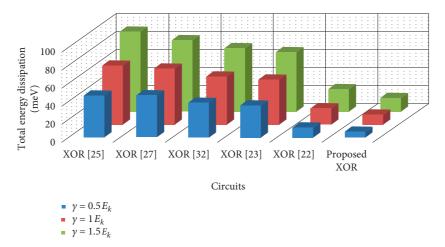

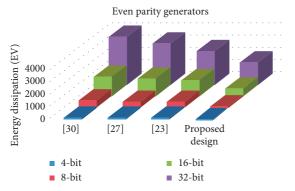

The OCADesigner tool version 2.0.3 is used to verify the functionality of the designed QCA circuits. The utilized parameters for the simulation are as follows: cell width = 18 nm, cell height = 18 nm, dot diameter = 5 nm, number of samples = 12.800, convergence tolerance = 0.001, radius of effect = 80 nm, relative permittivity = 12.9, high = 9.8E - 22J, clock low = 3.8E - 23J, clock amplitude factor = 2, layer separation = 11.5 nm, and maximum iterations per sample = 100. Table 1 shows the comparison results of the proposed exclusive-OR gate with previously reported XOR gates. The comparison is carried out considering the cell count and total area as well as latency of the circuit. As can be seen from Table 1, the proposed XOR circuit has less number of cells and reduced device area in comparison with the existing circuits. In Table 2, the proposed parity generator circuits have been compared with previously reported parity generator circuits [23, 25, 28–30]. Clearly, our designs outperform the proposed designs in [23, 25, 28–30]. In this work, QCAPro software [31], a probabilistic designing engine, has been applied for the energy depletion study. The power dissipation map of the proposed XOR gate is depicted in Figure 6(b). According to Figure 6(b), the darker cells exhibit higher average power dissipation and white squares represent the input cells. Table 3 illustrates the power consumed by the proposed QCA XOR design. The estimation is performed at temperature T = 2 K by employing three channeling energy levels, namely,  $0.5E_k$ ,  $1.0E_k$ , and  $1.5E_k$ . As is shown in Figure 9, our proposed gate has the lowest energy dissipation value at three separate tunneling energy levels as compared with the circuits in [22, 23, 25, 27, 32]. Consequently, the use of the proposed XOR gate in the design of parity generator circuits will provide more power savings. It is noticeable from Figure 10 that, our proposed architectures have least energy dissipation value in diverse sizes (4, 8, 16, and 32 bits) compared to existing

The power consumption of the proposed circuits is analyzed with the Hartree-Fock approximation [33]. The Hamiltonian matrix of a mean-field approach is explained as

$$H = \begin{bmatrix} \frac{-E_k}{2} \sum_{i} C_i f_i, j & -\gamma \\ -\gamma & \frac{E_k}{2} \sum_{i} C_i f_i, j \end{bmatrix}$$

$$= \begin{bmatrix} \frac{-E_k}{2} \left( C_{j-1} + C_{j+1} \right) & -\gamma \\ -\gamma & \frac{-E_k}{2} \left( C_{j-1} + C_{j+1} \right) \end{bmatrix}.$$

(3)

The kink energy cost of two neighboring cells i and j with opposite polarizations is derived as follows:

Table 1: Comparison of the proposed exclusive-OR gate with the previous work.

| Circuit         | Cell<br>count | Area<br>(μm²) | Clock<br>no.cycle | Crossover<br>type |

|-----------------|---------------|---------------|-------------------|-------------------|

| XOR [28]        | 60            | 0.09          | 1.5               | Coplanar          |

| XOR [29]        | 54            | 0.08          | 1.5               | Coplanar          |

| XOR [30]        | 67            | 0.06          | 1.25              | Coplanar          |

| XOR [25]        | 37            | 0.03          | 1                 | Not required      |

| XOR [24]        | 36            | 0.03          | 0.75              | Not required      |

| XOR [23]        | 28            | 0.02          | 0.75              | Not required      |

| XOR [22]        | 13            | 0.012         | 0.5               | Not required      |

| XOR [22]        | 12            | 0.011         | 0.5               | Not required      |

| Proposed<br>XOR | 9             | 0.01          | 0.5               | Not required      |

TABLE 2: Comparison results of parity generators.

| Circuit         | No of bits | Cell count | Area (µm²) | Clock<br>no.cycle |

|-----------------|------------|------------|------------|-------------------|

|                 | 4          | 187        | 0.32       | 2.75              |

| [20]            | 8          | 465        | 0.92       | 4                 |

| [28]            | 16         | 1024       | 2.41       | 5.25              |

|                 | 32         | 2220       | 5.96       | 6.5               |

|                 | 4          | 168        | 0.28       | 2.75              |

| [20]            | 8          | 408        | 0.8        | 4                 |

| [29]            | 16         | 912        | 2.09       | 5.25              |

|                 | 32         | 1968       | 5.16       | 6.5               |

|                 | 4          | 188        | 0.2        | 2.25              |

| [20]            | 8          | 369        | 0.49       | 2.25              |

| [30]            | 16         | 847        | 1.46       | 3.25              |

|                 | 32         | 1862       | 3.58       | 4.25              |

|                 | 4          | 111        | 0.14       | 2                 |

| [25]            | 8          | 269        | 0.43       | 3                 |

| [25]            | 16         | 603        | 1.13       | 4                 |

|                 | 32         | 1,312      | 2.81       | 5                 |

|                 | 4          | 87         | 0.10       | 1.75              |

| [22]            | 8          | 213        | 0.30       | 2.75              |

| [23]            | 16         | 480        | 0.81       | 3.75              |

|                 | 32         | 1,044      | 2.08       | 4.75              |

|                 | 4          | 37         | 0.05       | 1.5               |

| Dranged design  | 8          | 97         | 0.18       | 2.5               |

| Proposed design | 16         | 227        | 0.50       | 3.5               |

|                 | 32         | 511        | 1.3        | 4.5               |

|                 |            |            |            |                   |

TABLE 3: Power dissipation analysis of the XOR gate.

| OCA circuit  | Dissipation of power $T = 2.0 \mathrm{K}$ |                 |                   |  |  |

|--------------|-------------------------------------------|-----------------|-------------------|--|--|

| QCA circuit  | $\gamma = 0.5E_k$                         | $\gamma = 1E_k$ | $\gamma = 1.5E_K$ |  |  |

| XOR [25]     | 46.99                                     | 66.54           | 89.51             |  |  |

| XOR [27]     | 47.28                                     | 62.39           | 80.34             |  |  |

| XOR [32]     | 39.06                                     | 53.63           | 71.08             |  |  |

| XOR [23]     | 36.20                                     | 50.28           | 66.58             |  |  |

| XOR [22]     | 11.36                                     | 18.42           | 26.02             |  |  |

| Proposed XOR | 6.7                                       | 11.29           | 16.19             |  |  |

$$E_{i,j} = \frac{1}{4\pi\varepsilon_0\varepsilon_r} \sum_{n=1}^4 \sum_{m=1}^4 \frac{q_i q_j}{|r_i - r_j|}.$$

(4)

For any instance, the power depletion of a QCA cell can be calculated as follows:

FIGURE 9: The total power dissipation of the presented XOR gate at three different tunneling energy levels (T = 2 K).

FIGURE 10: Power dissipation comparison between different size (4-, 8-, 16-, and 32-bit) parity generator designs.

$$P_{\text{Total}} = \frac{d}{dt}E = \frac{\overline{h}}{2} \left( \frac{d}{dt} \overrightarrow{\Gamma} \right) \cdot \overrightarrow{\lambda} + \frac{\overline{h}}{2} \overrightarrow{\Gamma} \left( \frac{d}{dt} \overrightarrow{\lambda} \right) = P_1 + P_2.$$

(5)

#### 6. Conclusion

Quantum-dot cellular automata (QCA) is an upcoming nanoscale technology with great prospect to provide compact circuits with low energy consumption compared to CMOS technology. In this paper, a novel design of exclusive-OR gate in the QCA technology has been presented. It is more preferable for QCA implementations, since it does not use any rotate cells and majority gates. It incredibly reduces the area. Even parity generator circuits were designed and analyzed using this proposed gate as a building block. The designed circuits were simulated and verified by using the QCADesigner tool version 2.0.3. The power dissipation of the proposed designs has been investigated using QCAPro tools. A comparison of various XOR gates and parity generator circuits with regards to cell count, area, and energy dissipation is analyzed in this paper. The comparison results show that the designed QCA circuits have significant improvement compared to other existing ones.

## **Data Availability**

The data used to support the findings of this study are available from the corresponding author upon request.

## **Conflicts of Interest**

The authors declare that they have no conflicts of interest.

### References

- [1] K. Bernstein, R. K. Cavin, W. Porod, A. Seabaugh, and J. Welser, "Device and architecture outlook for beyond CMOS switches," *Proceedings of the IEEE*, vol. 98, no. 12, pp. 2169–2184, 2010.

- [2] P. K. Bondyopadhyay, "Moore's law governs the silicon revolution," *Proceedings of the IEEE*, vol. 88, no. 1, pp. 78–81, 2002.

- [3] N. Z. Haron and S. Hamdioui, "Why is CMOS scaling coming to an END?," in *Proceedings of the 2008 3rd International Design and Test Workshop*, pp. 98–103, Monastir, Tunisia, December, 2008.

- [4] R. H. Dennard, F. H. Gaensslen, H.-N. Yu, V. Leo Rideovt, E. Bassous, and A. R. Leblanc, "Design of ion-implanted MOSFET's with very small physical dimensions," *IEEE Solid-State Circuits Society Newsletter*, vol. 12, no. 1, pp. 38–50, 2007.

- [5] International Technology Roadmap for Semiconductors, "Process integration devices and structures (PIDS)," 2011, http://www.itrs.net/Links/2011ITRS/Home2011.htm.

- [6] C. S. Lent, P. D. Tougaw, W. Porod, and G. H. Bernstein, "Quantum cellular automata," *Nanotechnology*, vol. 4, no. 1, pp. 49–57, 1993.

- [7] G. L. Snider, A. O. Orlov, I. Amlani et al., "Quantum-dot cellular automata: review and recent experiments (invited)," *Journal of Applied Physics*, vol. 85, no. 8, pp. 4283–4285, 1999.

- [8] S. W. Kim and E. E. Swartzlander, "Parallel multipliers for quantum-dot cellular automata," in *Proceedings of the 2009 IEEE Nanotechnology Materials and Devices Conference*, pp. 68–72, Traverse City, MI, USA, June 2009.

- [9] S. W. Kim and E. E. Swartzlander, "Multipliers with coplanar crossings for quantum-dot cellular automata," in *Proceedings* of the 10th IEEE International Conference on Nanotechnology, pp. 953–957, Seoul, Republic of Korea, August 2010.

- [10] M. Balali, A. Rezai, H. Balali, F. Rabiei, and S. Emadi, "To-wards coplanar quantum-dot cellular automata adders based on efficient three-input XOR gate," *Results in Physics*, vol. 7, pp. 1989–1995, 2017.

- [11] T. N. Sasamal, A. K. Singh, and A. Mohan, "Efficient design of reversible ALU in quantum-dot cellular automata," *Optik*, vol. 127, no. 15, pp. 6172–6182, 2016.

- [12] T. N. Sasamal, A. K. Singh, and U. Ghanekar, "Design of non-restoring binary array divider in majority logic-based QCA," *Electronics Letters*, vol. 52, no. 24, pp. 2001–2003, 2016.

- [13] M. Kianpour and R. S. Nadooshan, "A novel modular decoder implementation in quantum-dot cellular automata (QCA)," in Proceedings of the 2011 International Conference on Nanoscience, Technology and Societal Implications (NSTSI), pp. 1–5, Bhubaneswar, India, December 2011.

- [14] M. Kianpour and R. S. Nadooshan, "A novel quantum dot cellular automata X-bit × 32-bit SRAM," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 24, no. 3, pp. 827–836, 2016.

- [15] P. P. Chougule, B. Sen, and T. D. Dongale, "Realization of processing in-memory computing architecture using quantum dot cellular automata," *Microprocessors and Micro*systems, vol. 52, pp. 49–58, 2017.

- [16] C. S. Lent and G. L. Snider, "The development of quantum-dot cellular automata," in *Field-Coupled Nanocomputing: Para*digms, *Progress, and Perspectives*, N. G. Anderson and S. Bhanja, Eds., pp. 3–20, Springer, Berlin, Germany, 2014.

- [17] S. Angizi, S. Sayedsalehi, A. Roohi, N. Bagherzadeh, and K. Navi, "Design and verification of new *n*-bit quantum-dot synchronous counters using majority function-based JK flipflops," *Journal of Circuits Systems, and Computers*, vol. 24, no. 10, 2015.

- [18] C. S. Lent and P. D. Tougaw, "A device architecture for computing with quantum dots," *Proceedings of the IEEE*, vol. 85, no. 4, pp. 541–557, 1997.

- [19] V. Vankamamidi, M. Ottavi, and F. Lombardi, "Two-dimensional schemes for clocking/timing of QCA circuits," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 27, no. 1, pp. 34–44, 2008.

- [20] W. W. Liu, M. O'Neill, and E. E. Swartzlander, Quantum-Dot Cellular Automata, 2013.

- [21] L. Liang, L. Weiqiang, M. O'Neill, and E. E. Swartzlander, "QCA systolic array design," *IEEE Transactions on Computers*, vol. 62, no. 3, pp. 548–560, 2013.

- [22] M. Berarzadeh, S. Mohammadyan, K. Navi, and N. Bagherzadeh, "A novel low power Exclusive-OR via cell level-based design function in quantum cellular automata," *Journal of Computational Electronics*, vol. 16, no. 3, pp. 875–882, 2017.

- [23] G. Singh, R. K. Sarin, and B. Raj, "A novel robust exclusive-OR function implementation in QCA nanotechnology with energy dissipation analysis," *Journal of Computational Electronics*, vol. 15, no. 2, pp. 455–465, 2016.

- [24] M. G. Waje and P. K. Dakhole, "Design and simulation of new XOR gate and code converters using quantum dot cellular automata with reduced number of wire crossings," in *Proceedings of the 2014 International Conference on Circuits*, *Power and Computing Technologies (ICCPCT-2014)*, pp. 1245–1250, Nagercoil, India, March 2014.

- [25] M. Poorhosseini and A. R. Hejazi, "A fault-tolerant and efficient XOR structure for modular design of complex QCA circuits," *Journal of Circuits, Systems and Computers*, vol. 27, no. 7, Article ID 1850115, 2018.

- [26] A. N. Bahar, S. Waheed, N. Hossain, and M. Asaduzzaman, "A novel 3-input XOR function implementation in quantum dot-cellular automata with energy dissipation analysis," *Alexandria Engineering Journal*, vol. 57, no. 2, pp. 729–738, 2017.

- [27] S. Sheikhfaal, S. Angizi, S. Sarmadi, M. Hossein Moaiyeri, and S. Sayedsalehi, "Designing efficient QCA logical circuits with power dissipation analysis," *Microelectronics Journal*, vol. 46, no. 6, pp. 462–471, 2015.

- [28] M. T. Niemier, "Designing digital systems in quantum cellular automata," M.S. thesis, University of Notre Dame, Notre Dame, IN, USA, 2004.

- [29] S. Hashemi, R. Farazkish, and K. Navi, "New quantum dot cellular automata cell arrangements," *Journal of Computational and Theoretical Nanoscience*, vol. 10, no. 4, pp. 798–809, 2013.

- [30] S. Angizi, E. Alkaldy, N. Bagherzadeh, and K. Navi, "Novel robust single layer wire crossing approach for exclusive or sum of products logic design with quantum-dot cellular automata," *Journal of Low Power Electronics*, vol. 10, no. 2, pp. 259–271, 2014.

- [31] S. Srivastava, A. Asthana, S. Bhanja, and S. Sarkar, "QCAP-ro—an error-power estimation tool for QCA circuit design," in *Proceedings of the 2011 IEEE International Symposium of Circuits and Systems (ISCAS)*, pp. 2377–2380, Rio de Janeiro, Brazil, May 2011.

- [32] T. N. Sasamal, A. K. Singh, and U. Ghanekar, "Design and analysis of ultra-low power QCA parity generator circuit," *Advances in Power Systems and Energy Management*, Vol. 436 of Lecture Notes in Electrical Engineering, pp. 341–354, Springer, Singapore, 2018.

- [33] J. Timler and C. S. Lent, "Power gain and dissipation in quantum-dot cellular automata," *Journal of Applied Physics*, vol. 91, no. 2, pp. 823–831, 2002.

Submit your manuscripts at www.hindawi.com